6Gbps mSATA FPGA Interface Project

Introduction

The goal of this project is to implement a SATA memory controller core on an Field Programmable Gate Array (FPGA) to facilitate high speed data transfer from the FPGA fabric to a non-volatile memory device. The project will rely on the SATA protocol, or Serial AT Attachment protocol.

SATA is a protocol that specifies how a host (in this case an FPGA) can communicate with a client device like a hard drive or solid state drive.

The SATA protocol specifies the valid commands and states that host and client can take while transferring data back and forth. Most people might be familiar with SATA from having used it in a computer, since it is the standard protocol a computer uses to read and write data to a hard drive.

This project aims, in particular, to support the SATA 3.1 protocol standard. The 3.1 standard specifies a link speed of 6 Gbps (allowing for a maximum data transmission speed, with overhead, of about 500 MBps) and also supports the smaller form factor of an mSATA drive.

A picture of the Solid State Drive that will be used with this project, a Samsung 850 EVO 1TB Drive

Ultimately, the goal of this project is to fill a crucial hole that currently exists in FPGA designs, namely an inability to store data at high speeds. FPGAs are excellent at dealing with lots of data in parallel, and this has led to their widespread use processing real time, high bandwidth data in fields like image processing and networking. In general, it's easy to deal with these large data rates in fabric, and a fairly typical FPGA can handle data on the order of 1-50 GBps in real time. The problem occurs when the application needs to save data, as no memory links are readily available that can handle this bandwidth of data to save it to a non-volatile medium. By implementing a SATA memory controller core on the FPGA, this project will allow FPGAs to save data as needed at high speeds to a nonvolatile memory device.

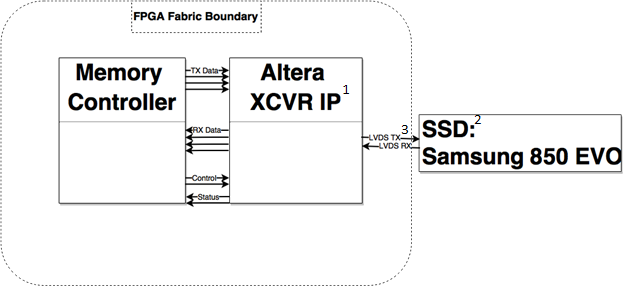

This project will deliver a Memory Controller Core, written in VHDL and tested on a Cyclone V ST FPGA, that will follow the high level diagram pictured below. The final project will write data to an SSD, and read back and verify the data it has written.

High Level Block Diagram of the Memory Controller IP.

XCVR: Altera Transceivers; IP: Intellectual Property; SSD: Solid State Drive; LVDS Rx/Tx: Low Voltage Differential Signal Receive/Transmit

Motivation

The motivation for this project was provided by Resonon, Inc in the form of two separate applications. The first is to collect and store imaging data on an Unmanned Aerial Vehicle (UAV). An airborne hyperspectral imaging system is being created that has a data output of approximately 45MB/s, and a way to capture this data in non-volatile memory is needed so it can be stored and processed offline. Another desired application is the Waterfall Sorting Project. This system uses both a hyperspectral and monochrome camera to capture data on lentils as they fall through the air, and ejects undesirable lentils from the main stream using air jets. The final system will use a machine learning algorithm that will require the ability to store the imaging data during the training process. The imaging components of this system will output data at a rate greater than the rough maximum of 500 MB/s that modern commercial Solid State Drives (SSDs) can achieve. The proposed solution is to implement a memory controller on a Field Programmable Gate Array (FPGA). FPGAs are very effective at processing image data, because of their inherent parallel nature, and this advantage could be leveraged to write to multiple SSDs at once, overcoming the physical limit on write bandwidth imposed by the SSD performance.

Project Goals

- Primary Objective

- The overarching goal of this project is to build a functional memory transfer prototype

instantiated on the Cyclone V ST FPGA that can read and write binary data to a Samsung

850 EVO mSATA SSD device.

- The overarching goal of this project is to build a functional memory transfer prototype

instantiated on the Cyclone V ST FPGA that can read and write binary data to a Samsung

850 EVO mSATA SSD device.

- Memory Abstraction

- In order for the controller to be most useful, the interface will be abstracted to

appear like a standard memory form such as FIFO (First In First Out). The standard

memory wrapper enables ease of integration with other devices, thereby improving the

usability of the controller since a potential user does not need to understand the

specifics of the product to implement it.

- In order for the controller to be most useful, the interface will be abstracted to

appear like a standard memory form such as FIFO (First In First Out). The standard

memory wrapper enables ease of integration with other devices, thereby improving the

usability of the controller since a potential user does not need to understand the

specifics of the product to implement it.

- Data Rate Saturation

- The controller interfaces with the Samsung SSD 850 EVO mSATA memory device, which

has a maximum capacity of 500 MB/s. Although the Level One Requirements of this project

do not mandate saturation of this link, a higher level goal is to approach this value

in order to optimize the solution.

- The controller interfaces with the Samsung SSD 850 EVO mSATA memory device, which

has a maximum capacity of 500 MB/s. Although the Level One Requirements of this project

do not mandate saturation of this link, a higher level goal is to approach this value

in order to optimize the solution.

- Parallelization

- In real world applications, it is expected that data rates may exceed 500 MB/s. To

increase the transfer link rate, multiple SSDs could be written to in parallel. The

FPGA has nine available transceivers, so this goal could be realized within hardware

constraints; an important consideration for the feasibility of this optional goal

is the power consumption increase due to the increased use of transceivers.

- In real world applications, it is expected that data rates may exceed 500 MB/s. To

increase the transfer link rate, multiple SSDs could be written to in parallel. The

FPGA has nine available transceivers, so this goal could be realized within hardware

constraints; an important consideration for the feasibility of this optional goal

is the power consumption increase due to the increased use of transceivers.

- Design Efficiency

- Ideally, the HDL design would minimize FPGA utilization. This would conserve power, leave processing capability available for other needs, and be an overall more efficient design. While this objective is not strictly required for the prototype to perform its function as a technology demonstration, minimizing device utilization would enable the prototype to more closely resemble the ultimate product, so it remains a project goal.

Advisor & Sponsor Information

Professor Ross Snider | College of Engineering

Dr. Snider joined the Electrical and Computer Engineering Department at Montana State University in August 1999. His research interests are focused on a combination of biology, signal processing, and computer engineering.

Tel: (406) 994-1645

Email: rksnider@ece.montana.edu