Background Information

What Is DRAM?

DRAM

is a type of dynamic RAM memory that utilizes the charge of a capacitor

to store ones and zeros. A single piece of DRAM is composed of a

large two dimensional array of cells containing ones or zeros that are

connected by bitlines and wordlines. Each individual cell can be

accessed by utilizing the intersection of a specific wordline and

bitline, and reading from or storing to the cell at this address.

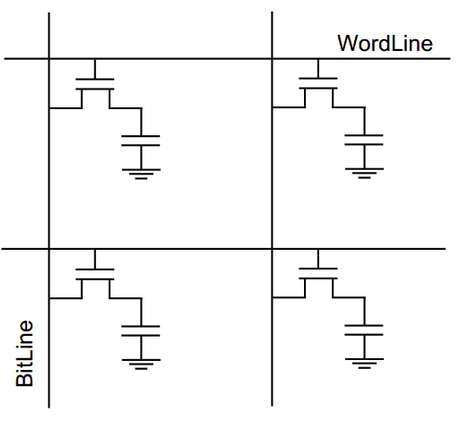

In

the idealized model, a single transistor and a single capacitor are

used to form a cell. When the wordline of the cell is high, the

transistor turns on and the capacitor can be written to or read from on

the bit line. Handy though this model is for understanding the

addressing of the cells, it would not work if it was implemented.

Figure 1

Figure 1

Idealized DRAM, and the problems with it

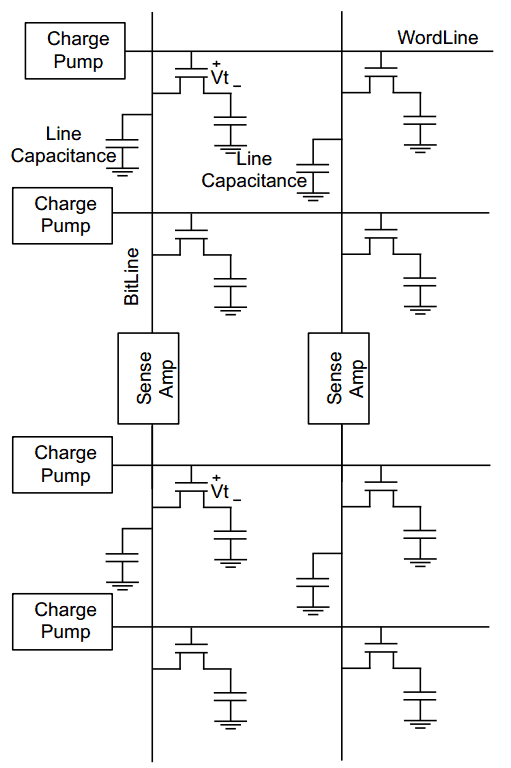

Figure 2Realistic DRAM model

Figure 2Realistic DRAM model

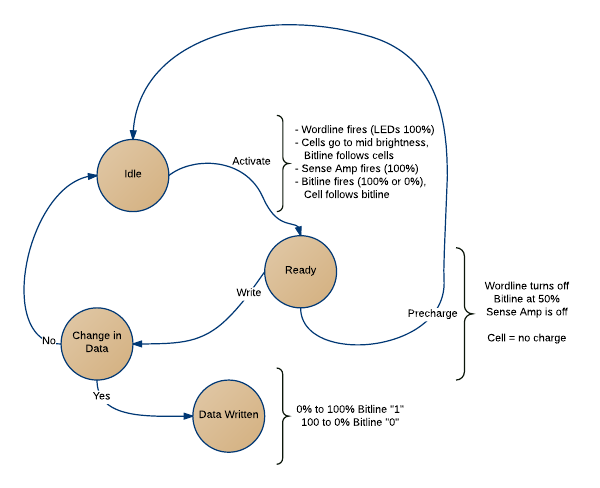

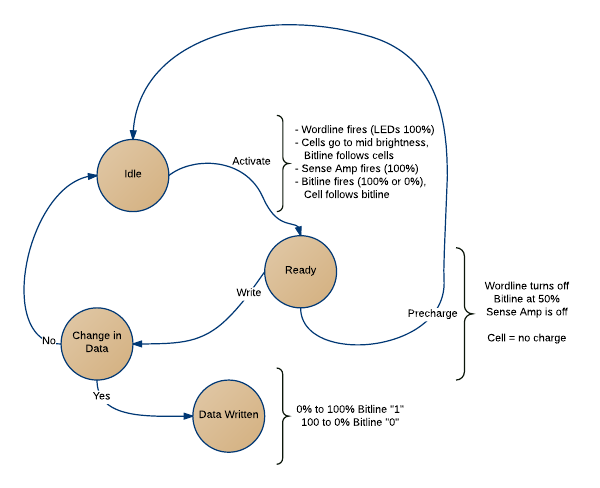

Figure 3Flowchart of what happens to the LEDs iin the process of a write and read

Figure 3Flowchart of what happens to the LEDs iin the process of a write and read

This

shows the working of a single cell, but during DRAM fabrication there

is always the chance of creating a cell that doesn't work. For

this eventuality excess cells are created in the array. If a

computer tries to read from or write to a broken cell it detects that the cell is broken and rewrites the address of that cell to one of the excess cells.